Super Micro Computer, Inc.

# Memory Configuration Guide

X9 Socket R Series DP Motherboards

## Introduction

This document is designed to provide the reader with an easy-to-use guide for proper memory configuration in an X9 based system.

#### **Memory Insertion Order**

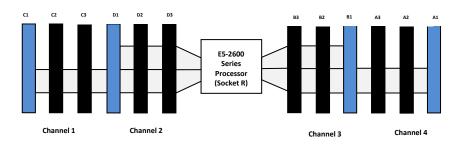

X9 DIMM's are populated using the "Fill First" method. The DIMM slot within a channel which is located the *farthest* from the processor is populated *first*. This is DIMM slot 0 and it is always denoted by its blue connector color. Additionally, when populating a quad-rank DIMM with a single or dual-rank DIMM in the same channel, the quad-rank DIMM must be populated farthest from the processor.

Table 1 DIMM insertion order (12 DIMM per CPU example)

| # DIMMs        | Population Order |                 |                 |  |

|----------------|------------------|-----------------|-----------------|--|

| per<br>Channel | DIMM2            | DIMM1           | DIMM0           |  |

| 3              | 3 <sup>rd</sup>  | 2 <sup>nd</sup> | 1 <sup>st</sup> |  |

| 2              | -                | 2 <sup>nd</sup> | 1 <sup>st</sup> |  |

| 1              | -                | -               | 1 <sup>st</sup> |  |

### A Few Rules to Keep Closely in Mind:

- All DIMMs must be DDR3

- Unbuffered DIMMs can be ECC or non-ECC

- A maximum of 8 logical ranks per channel is allowed

- Mixing of Registered and Unbuffered DIMMs is not allowed

- Mixing of ECC and non-ECC is not allowed

- Mixing of LRDIMM with any other DIMM type is not allowed

- Mixing of DDR3 voltages in **not advised**. If regular and low voltage DIMM's are mixed, the DIMMs will run as regular DIMMs

- Mixing of different DDR3 operating frequencies is **not advised**. If DIMM's with different frequencies are mixed, *all DIMMs will run at the lowest common frequency*

#### What is DIMM ranking?

The Intel® Xeon® E5-2600/2400 architecture has a maximum number of "logic" ranks per memory channel which limits how many physical DIMMs may be used for any given configuration. The processor can only "see" up to eight logical ranks per channel, therefore whatever combination of DIMMs that are physically added they can never exceed this limit. RDIMMs and UDIMMs typically come in single, dual, or quad rank configurations. The examples below demonstrate this effect.

**Table 2 Quad Rank RDIMM Example**

| Processor Memory      | Logical       | DIMM          | DIMM RDIMM/RDIMM-LV Quad Rank |          |       |

|-----------------------|---------------|---------------|-------------------------------|----------|-------|

| Channel<br>(Socket R) | Rank<br>Limit | Rank<br>Total | DIMM1                         | DIMM2    | DIMM3 |

| Channel 1             | 8             | 8             | 800/1066                      | 800/1066 | -     |

| Channel 2             | 8             | 8             | 800/1066                      | 800/1066 | -     |

| Channel 3             | 8             | 8             | 800/1066                      | 800/1066 | -     |

| Channel 4             | 8             | 8             | 800/1066                      | 800/1066 | -     |

As illustrated in the table above, only two of the quad ranked RDIMMs could be populated per channel without violating the Processors logical rank limit. Because of this DIMM3 is intentionally left unpopulated. Had it been populated, the rank total would have exceeded the logical rank limit of the processor and would not have been recognized by the Processor.

**Table 3 Quad Rank LRDIMM Example**

| Processor Memory      | Logical       | DIMM          | LRDIMM/LRDIMM-LV Quad Rank |           |           |

|-----------------------|---------------|---------------|----------------------------|-----------|-----------|

| Channel<br>(Socket R) | Rank<br>Limit | Rank<br>Total | DIMM1                      | DIMM2     | DIMM3     |

| Channel 1             | 8             | 8 6           | 1066/1333                  | 1066/1333 | 1066/1066 |

| Chamier 1             | J             |               | 1066/1333                  | 1066/1333 |           |

| Channel 2             | 8             | 6             | 1066/1333                  | 1066/1333 | 1066/1066 |

| Chamilei 2            | 0             | U             | 1066/1333                  | 1066/1333 | 1000/1000 |

| Channel 3             | Channel 3 8   | 6             | 1066/1333                  | 1066/1333 | 1066/1066 |

| Chamilers             | O             | U             | 1066/1333                  | 1066/1333 | 1000/1000 |

| Channel 4             | 8             | 6             | 1066/1333                  | 1066/1333 | 1066/1066 |

| Channel 4             | 0             | O             | 1066/1333                  | 1066/1333 | 1000/1000 |

Because LRDIMM are buffered, the processor only sees half of the LRDIMMs physical ranks. So a quad ranked LRDIMM appears to the Processor as a dual rank DIMM. Because of this it's possible to populate all three DIMM slots without violating the logical limit. However by doing so, the memory speed drops to 1066MHz as a result of the added memory. When using an Octal LRDIMM, DIMM3 would not be populated since filling DIMM1/DIMM2 would reach the logical rank limit of the processor.

# **Socket R Memory Configuration**

Four channels per socket, up to 3 DIMMS per Channel, and speeds up to DDR3 1600MHz

# Maximum Number of DIMM's support per CPU

| Ranks per DIMM | Maximum UDIMMs per<br>CPU | Maximum RDIMMs per<br>CPU | Maximum LRDIMMs per<br>CPU* |

|----------------|---------------------------|---------------------------|-----------------------------|

| Octal          | Not Supported             | Not Supported             | 8                           |

| Quad           | Not Supported             | 8                         | 12                          |

| Dual           | 8                         | 12                        | Not Supported               |

| Single         | 8                         | 12                        | Not Supported               |

<sup>\*</sup>LRDIMM ranks appear as half the number of ranks available to the CPU. For example, an 8-rank LRDIMM appears as a 4-rank.

# Maximum memory speed

When populating DIMM modules it's important to evenly distribute the modules across the channels. For example, if each CPU has four DIMMs populated, put one DIMM in Channel 1, Channel 2, Channel 3, and Channel 4 respectively. If each CPU has six DIMMs populated. Put the fifth DIMM in Channel 1 and the sixth in Channel 2.

#### Socket R:

| DIMM slots present per CPU | DIMM Type         | DIMM modules populated per CPU | Ranks per DIMM | Memory speeds supported |

|----------------------------|-------------------|--------------------------------|----------------|-------------------------|

|                            | UDIMM             | 1 to 4                         | Single or dual | 1066, 1333, 1600        |

|                            |                   | 5 to 8                         | Single or dual | 1066, 1333              |

|                            |                   | 9 to 12                        | Not supported  | Not supported           |

|                            |                   | 1 to 4                         | Single or dual | 1066, 1333, 1600        |

|                            | Low-voltage UDIMM | 5 to 8                         | Single or dual | 1066                    |

|                            |                   | 9 to 12                        | Not supported  | Not supported           |

|                            |                   | 1 to 4                         | Single or dual | 1066, 1333, 1600        |

|                            | RDIMM             |                                | Quad           | 1066                    |

| 12                         |                   | 5 to 8                         | Single or dual | 1066, 1333, 1600        |

| 12                         |                   |                                | Quad           | 800                     |

|                            |                   | 9 to 12                        | Single or dual | 800, 1066               |

|                            | Low-voltage RDIMM | 1 to 4                         | Single or dual | 1066, 1333              |

|                            |                   |                                | Quad           | 800                     |

|                            |                   | 5 to 8                         | Single or dual | 1066, 1333              |

|                            |                   |                                | Quad           | 800                     |

|                            |                   | 9 to 12                        | Not supported  | Not supported           |

|                            | LRDIMM*           | 1 to 4                         | Quad or Octal  | 1066, 1333              |

|                            |                   | 5 to 8                         | Quad or Octal  | 1066, 1333              |

|   |                       | 9 to 12 | Quad           | 1066             |

|---|-----------------------|---------|----------------|------------------|

|   | Low-voltage LRDIMM    | 1 to 4  | Quad or Octal  | 1066, 1333       |

|   |                       | 5 to 8  | Quad or Octal  | 1066             |

|   |                       | 9 to 12 | Quad           | 1066             |

|   | UDIMM                 | 1 to 4  | Single or dual | 1066, 1333       |

|   |                       | 5 to 8  | Single or dual | 1066, 1333       |

|   | Low-voltage UDIMM     | 1 to 4  | Single or dual | 1066, 1333       |

|   | Low-voitage Obliviivi | 5 to 8  | Single or dual | 1066, 1333       |

|   |                       | 1 to 4  | Single or dual | 1066, 1333, 1600 |

|   | DDIMAA                | 1 (0 4  | Quad           | 1066             |

|   | RDIMM                 |         | Single or dual | 1066, 1333, 1600 |

| 8 |                       | 5 to 8  | Quad           | 800              |

| 0 |                       | 1 to 4  | Single or dual | 1066, 1333       |

|   | Low-voltage RDIMM     |         | Quad           | 800              |

|   |                       | 5 to 8  | Single or dual | 1066, 1333       |

|   |                       |         | Quad           | 800              |

|   | LRDIMM                | 1 to 4  | Quad or Octal  | 1066, 1333       |

|   | LKDIIVIIVI            | 5 to 8  | Quad or Octal  | 1066, 1333       |

|   | Low-voltage LRDIMM    | 1 to 4  | Quad or Octal  | 1066             |

|   |                       | 5 to 8  | Quad or Octal  | 1066             |

|   | UDIMM                 | 1 to 4  | Single or dual | 1066, 1333, 1600 |

| 4 | Low-voltage UDIMM     | 1 to 4  | Single or dual | 1066, 1333       |

|   | RDIMM                 | 1 to 4  | Single or dual | 1066, 1333, 1600 |

|   |                       |         | Quad           | 1066             |

|   | Low-voltage RDIMM     | 1 to 4  | Single or dual | 1066, 1333       |

|   |                       | 1 10 4  | Quad           | 800              |

|   | LRDIMM                | 1 to 4  | Quad or Octal  | 1066, 1333       |

|   | Low-Voltage LRDIMM    | 1 to 4  | Quad or Octal  | 1066, 1333       |

# **DDR3 DIMM Modules Mechanical Specification**

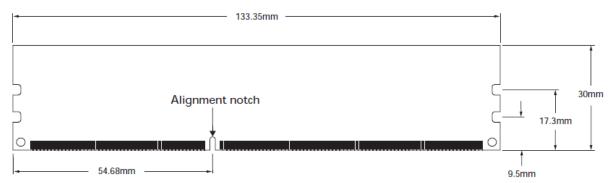

# Standard:

#### **Features**

- 30mm x 133.35mm

- 240 pins

- 1.5V/1.35V (Low-Voltage)Unbuffered or registered

- x64/x72

- JEDEC MO-269

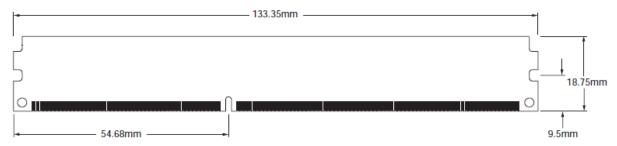

# Low Profile:

#### **Features**

- 18.75mm x 133.35mm

- 240 pins

- 1.5V/1.35V (Low-Voltage)Unbuffered or registered

- x64/x72

- JEDEC MO-269