# SUPERMICRO® SuperWorkstation 7037A-i Quick Reference Guide

## Board Layout

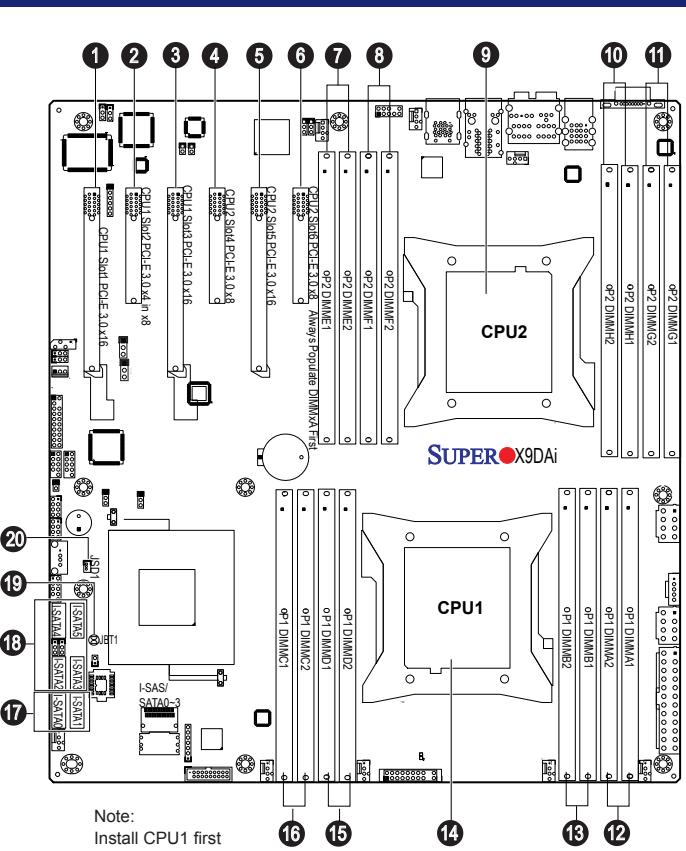

| No. | Description                   |

|-----|-------------------------------|

| 1   | CPU1 Slot1 PCI-E 3.0 x16      |

| 2   | CPU1 Slot2 PCI-E 3.0 x4 in x8 |

| 3   | CPU1 Slot3 PCI-E 3.0 x16      |

| 4   | CPU2 Slot4 PCI-E 3.0 x8       |

| 5   | CPU2 Slot5 PCI-E 3.0 x16      |

| 6   | CPU2 Slot6 PCI-E 3.0 x8       |

| 7   | P2 DIMME1/P2 DIMME2           |

| 8   | P2 DIMMF1/P2 DIMMF2           |

| 9   | CPU2                          |

| 10  | P2 DIMMH1/P2 DIMMH2           |

| No. | Description               |

|-----|---------------------------|

| 11  | P2 DIMMG1/P2 DIMMG2       |

| 12  | P1 DIMMA1/P1 DIMMA2       |

| 13  | P1 DIMMB1/P1 DIMMB2       |

| 14  | CPU1 (Install CPU1 first) |

| 15  | P1 DIMMD1/P1 DIMMD2       |

| 16  | P1 DIMMC1/P1 DIMMC2       |

| 17  | SATA 0/1 = SATA 3.0 Ports |

| 18  | SATA 2~5 = SATA 2.0 Ports |

| 19  | JBT1 = CMOS Reset         |

| 20  | JSD1= SATA DOM Power      |

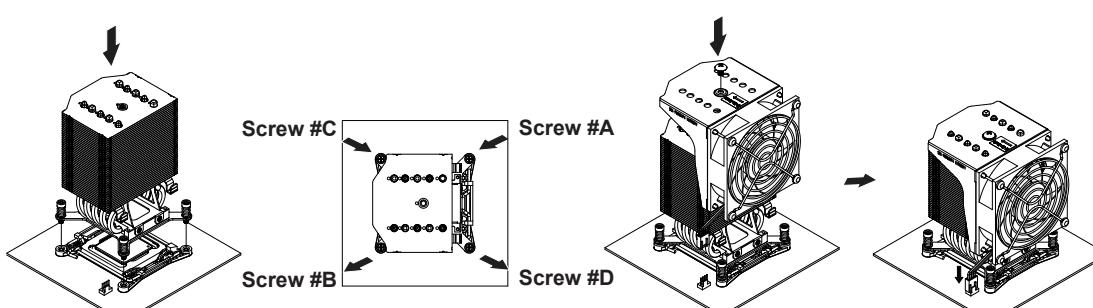

## Heatsink Installation

1. Place heatsink on top of installed CPU

2. Line up the four screws to socket

3. Push down heatsink and screw down as shown (cross pattern, in order: A, B, C, D)

4. NOTE: Only use 6-8 lb/f of torque; otherwise, hand-tighten each screw, to avoid damaging the system

## MEMORY

| CPU#  | Processors and their Corresponding Memory Modules |           |           |           |           |           |           |

|-------|---------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

|       | Corresponding DIMM Modules                        |           |           |           |           |           |           |

| CPU 1 | P1-DIMMA1                                         | P1-DIMMB1 | P1-DIMMC1 | P1-DIMMD1 | P1-DIMMA2 | P1-DIMMB2 | P1-DIMMC2 |

| CPU 2 | P2-DIMME1                                         | P2-DIMMF1 | P2-DIMMG1 | P2-DIMMH1 | P2-DIMME2 | P2-DIMMF2 | P2-DIMMG2 |

| Processors and Memory Module Population for Optimal Performance |  |                                                                                                                                                             |  |  |  |  |  |

|-----------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Number of CPUs + DIMMs                                          |  | CPU and Memory Population Configuration Table<br>(For memory to work properly, follow the instructions below)                                               |  |  |  |  |  |

| 1 CPU & 2 DIMMs                                                 |  | CPU1 & P1-DIMMA1/P1-DIMMB1                                                                                                                                  |  |  |  |  |  |

| 1 CPU & 4 DIMMs                                                 |  | CPU1 & P1-DIMMA1/P1-DIMMB1, P1-DIMMC1/P1-DIMMD1                                                                                                             |  |  |  |  |  |

| 1 CPU & 5-8 DIMMs                                               |  | CPU1 & P1-DIMMA1/P1-DIMMB1, P1-DIMMC1/P1-DIMMD1 + Any memory pairs in P1-DIMMA2/P1-DIMMB2/P1-DIMMC2/P1-DIMMD2 slot                                          |  |  |  |  |  |

| 2 CPUs & 4 DIMMs                                                |  | CPU1 + CPU2 & P1-DIMMA1/P1-DIMMB1, P2-DIMME1/P2-DIMMF1/P2-DIMMG1                                                                                            |  |  |  |  |  |

| 2 CPUs & 6 DIMMs                                                |  | CPU1 + CPU2 & P1-DIMMA1/P1-DIMMB1/P1-DIMMC1/P1-DIMMD1, P2-DIMME1/P2-DIMMF1/P2-DIMMG1                                                                        |  |  |  |  |  |

| 2 CPUs & 8 DIMMs                                                |  | CPU1 + CPU2 & P1-DIMMA1/P1-DIMMB1/P1-DIMMC1/P1-DIMMD1, P2-DIMME1/P2-DIMMF1/P2-DIMMG1/P2-DIMMH1                                                              |  |  |  |  |  |

| 2 CPUs & 10-16 DIMMs                                            |  | CPU1 + CPU2 & P1-DIMMA1/P1-DIMMB1/P1-DIMMC1/P1-DIMMD1/P1-DIMMA2, P2-DIMME1/P2-DIMMF1/P2-DIMMG1/P2-DIMMH1/P2-DIMME2, Any memory pairs in P1, P2 memory slots |  |  |  |  |  |

### Installing UDIMM (ECC/non-ECC) Memory

| Ranks per DIMM & Data Width | Memory Capacity Per DIMM (See the Note below) | Speed (MT/s) and Voltage Validated by Slot per Channel (SPC) and DIMM Per Channel (DPC) |  |            |  |  |

|-----------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|--|------------|--|--|

|                             |                                               | 2 Slots Per Channel                                                                     |  | 2DPC       |  |  |

|                             |                                               | 1.35V                                                                                   |  | 1.5V       |  |  |

| SRx8 Non-ECC                |                                               | NA                                                                                      |  | 1066, 1333 |  |  |

| DRx8 Non-ECC                |                                               | NA                                                                                      |  | 1066, 1333 |  |  |

| SRx16 Non-ECC               |                                               | NA                                                                                      |  | 1066, 1333 |  |  |

| SRx8 ECC                    |                                               | 1066, 1333                                                                              |  | 1066, 1333 |  |  |

| DRx8 ECC                    |                                               | 1066, 1333                                                                              |  | 1066, 1333 |  |  |

Notes:

1. 1 GB/2GB/4GB DRAMs are supported; however, only 2GB and 4 GB DRAMs are validated.

2. Command Address Timing is 1N for 1DPC an 2N for 2DPC.

3. ES-4600 4S platforms do not support 3DPC UDIMMs.

4. Please refer to the ES-460 Platform Design Guide for memory population rules.

### Installing RDIMM (ECC) Memory

| Ranks per DIMM & Data Width | Memory Capacity Per DIMM (See the Note below) | Speed (MT/s) and Voltage Validated by Slot per Channel (SPC) and DIMM Per Channel (DPC) (Note 2, 3, 4) |  |                     |  |  |

|-----------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|--|---------------------|--|--|

|                             |                                               | 1 Slot Per Channel                                                                                     |  | 2 Slots Per Channel |  |  |

|                             |                                               | 1.35V                                                                                                  |  | 1.5V                |  |  |

| SRx8                        |                                               | 1066, 1333                                                                                             |  | 1066, 1333          |  |  |

| DRx8                        |                                               | 1066, 1333                                                                                             |  | 1066, 1333          |  |  |

| SRx8                        |                                               | 1066, 1333                                                                                             |  | 1066, 1333          |  |  |

| DRx4                        |                                               | 1066, 1333                                                                                             |  | 1066, 1333          |  |  |

| QRx4 (DDP) (Note 7)         |                                               | 800                                                                                                    |  | 800                 |  |  |

| QRx8 (P) (Note 8)           |                                               | 1066, 1333                                                                                             |  | 1066, 1333          |  |  |

Notes:

1. 1 GB/2GB/4GB DRAMs are supported; however, only 2GB and 4 GB DRAMs are validated.

2. Command Address Timing is 1N for 1DPC an 2N for 2DPC.

3. Please refer to the ES-460 Platform Design Guide for memory population rules.

4. QR RDIMMs are supported but not validated. Memory testing are limited to system level testing. Singal integrity in interoperability testing are not performed. The passing QR RDIMMs will be posted on the website.

5. Please refer to the ES-460 Platform Design Guide for memory population rules.

6. For 3SPC/3DPC-Rank Multiplication (RM)  $16 \times 2 = 2$ .

7. DDP is for Dual Die Package DRAM stacking.

8. "P" Means "Planner Monolithic DRAM Die".

### Installing LRDIMM Memory

| Ranks per DIMM & Data Width | Memory Capacity Per DIMM (Note 2) | Speed (MT/s) and Voltage Validated by Slot Per Channel (SPC) and DIMM Per Channel (DPC) (Note 3, 4, 5, 6) |  |            |  |  |

|-----------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|--|------------|--|--|

|                             |                                   | 2 Slots Per Channel                                                                                       |  | 1DPC/2DPC  |  |  |

|                             |                                   | 1.35V                                                                                                     |  | 1.5V       |  |  |

| QRx4 (DDP) (Note 7)         |                                   | 1066                                                                                                      |  | 1066, 1333 |  |  |

| QRx8 (P) (Note 8)           |                                   | 1066                                                                                                      |  | 1066, 1333 |  |  |

Notes:

1. Physical Rank is used to calculate DIMM capacity.

2. Command Address Timing is 1N.

3. Only 2GB 4GB DRAMs are supported and validated.

4. The speeds listed are estimated only and will be verified through simulation.

5. Please refer to the ES-4600 Platform Design Guide for memory population rules.

6. For 3SPC/3DPC-Rank Multiplication (RM)  $16 \times 2 = 2$ .

7. DDP is for Dual Die Package DRAM stacking.

8. "P" Means "Planner Monolithic DRAM Die".

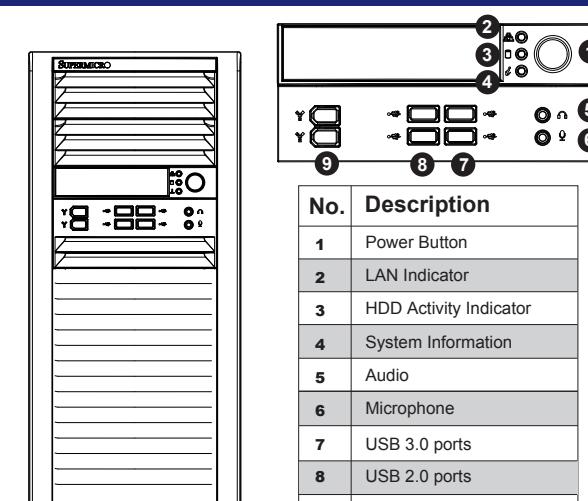

## Front View & Interface

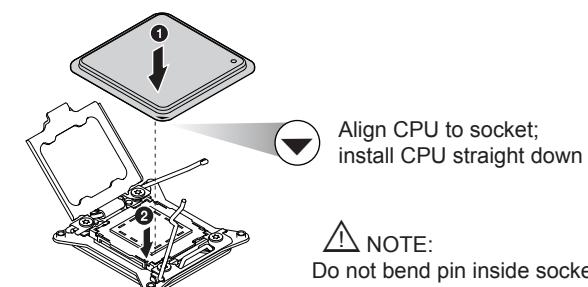

## CPU Installation

Align CPU to socket;

install CPU straight down