# MEMORY RAS CONFIGURATION

USER'S GUIDE

Revision 1.0

The information in this User's Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. **Please Note:** For the most up-to-date version of this manual, please see our website at www.supermicro.com.

Super Micro Computer, Inc. ("Supermicro") reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software and documentation, is the property of Supermicro and/ or its licensors, and is supplied only under a license. Any use or reproduction of this product is not allowed, except as expressly permitted by the terms of said license.

IN NO EVENT WILL Super Micro Computer, Inc. BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, SUPER MICRO COMPUTER, INC. SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA.

Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. Supermicro's total liability for all claims will not exceed the price paid for the hardware product.

FCC Statement: This equipment has been tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the manufacturer's instruction manual, may cause harmful interference with radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case you will be required to correct the interference at your own expense.

<u>California Best Management Practices Regulations for Perchlorate Materials</u>: This Perchlorate warning applies only to products containing CR (Manganese Dioxide) Lithium coin cells. "Perchlorate Material-special handling may apply. See www.dtsc.ca.gov/hazardouswaste/perchlorate".

<u>WARNING</u>: Handling of lead solder materials used in this product may expose you to lead, a chemical known to the State of California to cause birth defects and other reproductive harm.

The products sold by Supermicro are not intended for and will not be used in life support systems, medical equipment, nuclear facilities or systems, aircraft, aircraft devices, aircraft/emergency communication devices or other critical systems whose failure to perform be reasonably expected to result in significant injury or loss of life or catastrophic property damage. Accordingly, Supermicro disclaims any and all liability, and should buyer use or sell such products for use in such ultra-hazardous applications, it does so entirely at its own risk. Furthermore, buyer agrees to fully indemnify, defend and hold Supermicro harmless for and against any and all claims, demands, actions, litigation, and proceedings of any kind arising out of or related to such ultra-hazardous use or sale.

Manual Revision 1.0

Release Date: December 22, 2017

Unless you request and receive written permission from Super Micro Computer, Inc., you may not copy any part of this document. Information in this document is subject to change without notice. Other products and companies referred to herein are trademarks or registered trademarks of their respective companies or mark holders.

Copyright © 2017 by Super Micro Computer, Inc. All rights reserved. Printed in the United States of America

# **Chapter 1**

## Introduction

### About This User Guide

This user's guide is written for system integrators, IT technicians, and knowledgeable end users. It provides information on memory RAS support and configuration on a Supermicro motherboard or system.

#### Introduction to Reliability, Availability and Serviceability

Reliability, Availability, and Serviceability (RAS) is a computer-engineering architecture that promotes reliability engineering, high availability, and serviceability design. For product reliability, computer components or systems are designed to maintain consistent performance based on the specifications without deviations or errors. For system availability, a component or server will always function as it should, and it will also be constantly available for use with minimal downtime. For computer serviceability, a component or a system can be maintained or repaired with ease. With full implementation of RAS into our product design and system integration, Supermicro's computer systems are engineered to provide you with the highest standards in quality, performance, availability, and usability at all times.

### Introduction to Memory RAS Configuration

As a world's server manufacturer leader, Supermicro has integrated memory RAS features into our products to enhance data integrity and system performance and to prevent data alternation or data loss caused by electronic transactions for many years. Additionally, we've also built in layers of data-checking, error-detection, and error-correction mechanisms for memory error recovery to maximize storage and network security. The memory RAS capabilities that have been implemented into our products include memory mirroring, enhanced Error Checking and Correction (ECC), memory scrubbing, and memory sparing. In addition to these highly efficient memory protection mechanisms that are embedded in the integrated memory controllers of Supermicro computers, we've utilized the latest technology available in the industry to further enhance data integrity and system security for our systems. These new advanced RAS features include:

- SDDC: Single Device Data Correction

- SDDC+1: SDDC\_Plus\_One

- DDDC: Double Device Data Correction

- ADDDC: Adaptive Double Device Data Correction

# **Contacting Supermicro**

#### Headquarters

| Super Micro Computer, Inc.                     |

|------------------------------------------------|

| 980 Rock Ave.                                  |

| San Jose, CA 95131 U.S.A.                      |

| +1 (408) 503-8000                              |

| +1 (408) 503-8008                              |

| marketing@supermicro.com (General Information) |

| support@supermicro.com (Technical Support)     |

| www.supermicro.com                             |

|                                                |

|                                                |

| Super Micro Computer B.V.                      |

| Het Sterrenbeeld 28, 5215 ML                   |

| 's-Hertogenbosch, The Netherlands              |

| +31 (0) 73-6400390                             |

| +31 (0) 73-6416525                             |

| sales@supermicro.nl (General Information)      |

| support@supermicro.nl (Technical Support)      |

| rma@supermicro.nl (Customer Support)           |

| www.supermicro.nl                              |

|                                                |

|                                                |

| Super Micro Computer, Inc.                     |

| 3F, No. 150, Jian 1st Rd.                      |

| Zhonghe Dist., New Taipei City 235             |

| Taiwan (R.O.C)                                 |

| +886-(2) 8226-3990                             |

| +886-(2) 8226-3992                             |

| support@supermicro.com.tw                      |

| www.supermicro.com.tw                          |

|                                                |

# **Table of Contents**

#### Chapter 1 Introduction Chapter 2 Intel ECC Mode Common Technology

|     | SDDC                                                              | 6  |

|-----|-------------------------------------------------------------------|----|

|     | SDDC + 1                                                          | 7  |

|     | DDDC                                                              | 8  |

|     | DDDC+1                                                            | 9  |

|     | ADDDC                                                             | 9  |

|     | ADDDC+1 (Adaptive Double Device Data Correction Plus One)         | 9  |

|     | ADDDC (Adaptive Double Device Correction) Bank                    | 10 |

|     | ADDDC (Adaptive Double Device Correction) Rank                    | 11 |

|     | Physical/Logical DRAM Map, Rank VLS                               | 12 |

|     | Memory RAS DIMM Limitation                                        | 12 |

| Cha | apter 3 Configuring Memory RAS Features in the BIOS Setup Utility |    |

|     |                                                                   |    |

# Chapter 2

# Intel ECC Mode Common Technology

#### SDDC

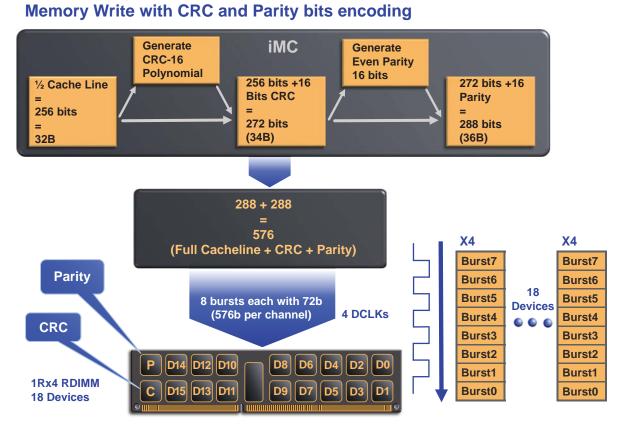

Single Device Data Correction (SDDC) checks and corrects single-bit or multiple-bit (4-bit max.) memory faults that affect an entire single x4 DRAM device.

# SDDC Algorithm Overview (1 of 3)

#### SDDC + 1

SDDC+1, which is the enhanced feature to SDDC, will spare the faulty DRAM device out after an SDDC event has occurred. After the event, the SDDC+1 ECC mode is activated to protect against any additional memory failure caused by a 'single-bit' error in the same memory rank.

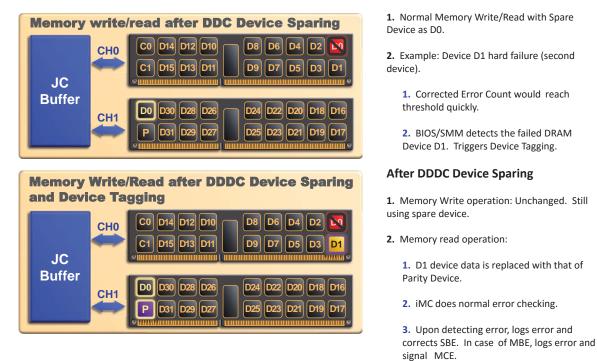

#### SDDC+1 Algorithm with Device Tagging

- 1. Normal Memory Write/Read

- Example: Device D0 hard failure.

Corrected Error Count would reach threshold quickly.

- 2. BIOS/SMM detects the failed DRAM Device D0. Triggers Device Tagging.

#### After Device Tagging

- 1. Memory Writer operation: Unchanged (Normal).

- **2.** Memory read operation:

- 1. D0 device data is replaced with that of Parity Device.

- 2. iMC does normal error Checking.

- **3.** Intel Xeon Scable Processor Family: Upon detecting error, logs error and signal MCE.

#### DDDC

Double Device Data Correction (DDDC) provides error checking and correction to protect against memory failures occurred to two, sequential, and x4 DRAM devices due to harderrors on DIMM modules. DDDC is supported only with x4 DRAMs and with two channels in the lockstep mode. (This feature is not supported for x8 DRAM device-based DIMM.)

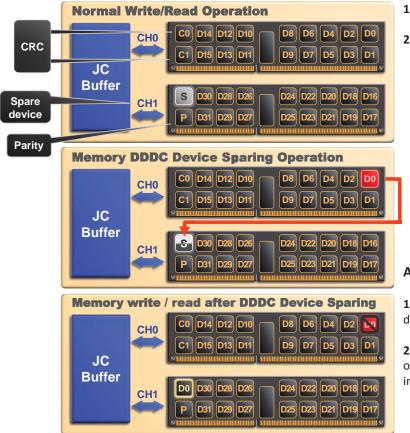

### Memory DDDC+1 Algorithm Overview (2 of 3)

- 1. Normal Memory Write/Read

- 2. Example: Device D0 hard failure.

**1.** Corrected Error Count would reach threshold quickly. SMI is triggered.

2. BIOS/SMM detects the failed DRAM Device D0. Triggers "DDDC Device Sparing event".

**3.** DDDC Device Sparing Engine copies data from D0 to spare device. SMI is triggered upon completion.

#### After DDDC Device Sparing

**1.** iMC disable any further "DDDC device sparing event"..

**2.** Normal Memory Write/Read operations always use Spare device instead of D0 Device.

#### DDDC+1

Double Device Data Correction (DDDC) Plus One allows the error correction code to correct an error caused by the failure of two DRAM devices or by a single-bit error that is beyond a device failure in the lockstep mode.

#### Memory DDDC+1 Algorithm Overview (3 of 3)

#### ADDDC

Adaptive Double Device Data Correction (ADDDC), which is an enhanced feature to DDDC, will not issue a performance penalty before a device fails. Please note that virtual lockstep mode will only start to work for ADDDC after a faulty DRAM module is spared out at Bank or Rank granularity.

#### ADDDC+1 (Adaptive Double Device Data Correction Plus One)

Adaptive Double Device Data Correction Plus One (ADDDC+1), which is an improved feature of ADDDC, will allow the error correction code to correct an error caused by the failure of two DRAM devices or by a single-bit error that is beyond a device failure in the lockstep mode. ADDDC+1 will not issue a performance penalty before a device fails. Please note that virtual lockstep mode will only start to work for ADDDC after a faulty DRAM module is spared out at Bank granularity or Rank granularity.

#### ADDDC (Adaptive Double Device Correction) Bank

If ADDDC Bank is implemented, a memory failure will only occur to a DRAM bank and will not occur to the whole device because a bank granularity of a DRAM region will enter into virtual lockstep (VLS) along with a buddy bank, allowing the content of the bank of a failing DRAM device to be copied over to the bank of the spare buddy device as soon as an error occurs to a good DIMM.

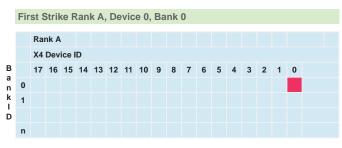

#### Adaptive DDDC (MR), Bank Virtual lockstep

Action: VLS the failed Bank, map out Device 0, Bank 0 by copying Content to bank 0 in spare DRAM Device.

|        | R | ank  | A    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |       | Rar | nk B | 5     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------|---|------|------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|-------|-----|------|-------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|        | х | 4 De | vice | ID |    |    |    |    |   |   |   |   |   |   |   |   |   |   |       | X4  | Dev  | ice I | D  |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| _      |   |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |       |     |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| В      | 1 | 7 1  | 5 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |       | 17  | 16   | 15    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| n      | 0 |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | <br>0 |     |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| k<br>I | 1 |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | 1     |     |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| D      |   |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |       |     |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|        | n |      |      |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   | n     |     |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

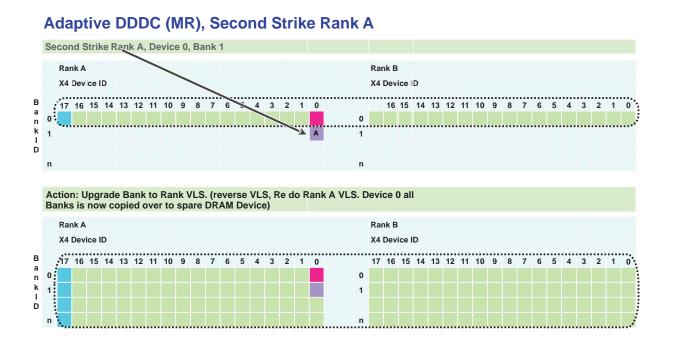

#### ADDDC (Adaptive Double Device Correction) Rank

If ADDDC Rank is implemented, device sparing at a rank granularity will be enabled to allow the content of the whole DRAM device to be copied to a spare device when a second saved DRAM device installed in another bank of the same memory channel fails.

SDDC + 1

- SDDC + 1 will occur if 'ADDDC spare' is enabled in the BIOS menu. This will only happen when another 'single device failure' occurs after an "ADDDC Rank' event, and the current ECC mode can correct an additional single bit error after SDDC spare is completed;

- SDDC + 1 will occur if 'ADDDC spare' is disabled, 'SDDC plus one' is enabled in the BIOS menu, and VLS is disabled. This mode is enabled after 'a single DRAM device failure' has occurred and the process of 'device spare' is completed. It can correct an additional single bit error in the ECC mode.

- SDDC + 1 will occur when a correctable memory error within one DRAM device bank exceeds the threshold, and ADDDC Bank Virtual Lock Step is active. Subsequently, a correctable memory error in any other bank will trigger "ADDDC Rank Virtual Lock Step", and it will trigger SDDC+1 in any other DRAM device as well.

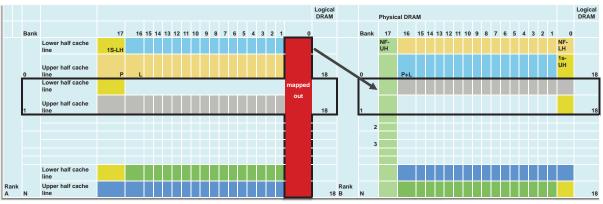

#### Physical/Logical DRAM Map, Rank VLS

Physical/logical DRAM Map, Rank VLS

Post Rank VLS: DRAM 0 is mapped out, Rank B device 17 holds Data Parity+Locator is combined into Device 16.

#### Memory RAS DIMM Limitation

| Memory RAS DIMM Limitation |               |                   |  |  |  |  |  |  |  |  |

|----------------------------|---------------|-------------------|--|--|--|--|--|--|--|--|

| DRAM Type                  | x4 DRAM DIMMS | x8 DRAM DIMM      |  |  |  |  |  |  |  |  |

| SDDC(+1)                   | Support       | Support (Note *1) |  |  |  |  |  |  |  |  |

| ADDDC(+1)                  | Support       | Not Support       |  |  |  |  |  |  |  |  |

**Note 1**: x8 Single Device Data Correction (SDDC) and SDDC+1 are supported only via 'static virtual lockstep'. Please be sure to enable 'Static Virtual Lockstep Mode' in the BIOS setup utility. Please be sure to install at least one x8DIMM module with two logical RANKs or two x8 DIMM modules with a single RANK each in a DDR channel.

**Note 2**: SDDC (+1) and ADDDC (+1) are not compatible with Mirroring and Rank Sparing. When Mirror or Rank Sparing is enabled, neither ADDDC nor SDDC will not be supported.

# Chapter 3

### Configuring Memory RAS Features in the BIOS Setup Utility

To configure the SDDC+1/ADDDC RAS settings in the BIOS, follow the instructions below:

1. Power on your computer and hit the <Delete> key continuously to enter the BIOS setup utility upon bootup as the screen shown below.

|                    | [Wed 12/13/2017] | Set the Date. Use Tab to switch between Date |

|--------------------|------------------|----------------------------------------------|

| ystem Time         | [14:48:34]       | elements.<br>Default Ranges:                 |

| upermicro X11DPH-T |                  | Year: 2005-2099                              |

| IOS Version        | 2.0a             | Months: 1-12                                 |

| uild Date          | 12/12/2017       | Days: dependent on month                     |

| PLD Version        | 02.86.01         |                                              |

| emory Information  |                  |                                              |

| otal Memory        | 32768 MB         |                                              |

|                    |                  |                                              |

|                    |                  |                                              |

|                    |                  |                                              |

|                    |                  |                                              |

|                    |                  | ++: Select Screen                            |

|                    |                  | 11: Select Item                              |

|                    |                  | Enter: Select                                |

|                    |                  | +/-: Change Opt.                             |

|                    |                  | F1: General Help                             |

|                    |                  | F2: Previous Values                          |

|                    |                  | F3: Optimized Defaults                       |

|                    |                  | F4: Save & Exit                              |

|                    |                  | ESC: Exit                                    |

2. Using the arrow keys, select the <Advanced> menu on the top of the screen and hit <Enter> to enter the Advanced submenu.

3. Using the down arrow key, scroll down to select the *Chipset Configuration* submenu and hit <Enter> as shown below.

| Aptio Setup Utility – Copyright (C) 2017 America<br>Main <mark>Advanced</mark> Event Logs IPMI Security Boot Save & Exi                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Boot Feature</li> <li>CPU Configuration</li> <li>Chipset Configuration</li> <li>Server ME Configuration</li> <li>PCH SATA Configuration</li> <li>PCH SATA Configuration</li> <li>PCIE/PCI/PrP Configuration</li> <li>Super 10 Configuration</li> <li>Serial Port Console Redirection</li> <li>ACPT Settings</li> <li>Trusted Computing</li> <li>ISCSI Configuration</li> <li>Intel(R) Virtual RAID on CPU</li> </ul> | System Chipset<br>configuration.<br>+t: Select Screen<br>11: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESC: Exit |

| Version 2.19.1268. Copyright (C) 2017 American                                                                                                                                                                                                                                                                                                                                                                                | Megatrends, Inc.                                                                                                                                                                                                   |

4. Select North Bridge and hit <Enter>. The following screen will display.

| UPI Configuration                         | Displays and provides                                                                                                                                                          |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Configuration<br>IIO Configuration | option to change the Memory<br>Settings                                                                                                                                        |

|                                           | ++: Select Screen<br>11: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESC: Exit |

5. Use the arrow key to select *Memory Configuration* and hit <Enter>. The following screen will display.

| Integrated Memory Controller (iMC)                                                                                                                                                                                                         |                                                                               | Displays and provides<br>option to change the Memory<br>Ras Settings                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enforce POR<br>Memory Frequency<br>Data Scrambling for NVMDIMM<br>Data Scrambling for DDR4<br>tCCD_L Relaxation<br>Memory tRMSR Relaxation<br>2X REFRESH<br>Page Policy<br>IMC Interleaving<br>Memory Topology<br>Memory RAS Configuration | [POR]<br>[Auto]<br>[Auto]<br>[Auto]<br>[Enable]<br>[Auto]<br>[Auto]<br>[Auto] |                                                                                                                                                                                |

|                                                                                                                                                                                                                                            |                                                                               | ++: Select Screen<br>11: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>FSC: Fxit |

6. Using the down arrow key, scroll down to select *Memory RAS Configuration* from the screen above and hit <Enter>. The following screen will display:

| Memory RAS Configuration Setup                                                                                                                                                                 |                                                                                                    | Enable/Disable SDDC Plus One                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static Virtual Lockstep Mode<br>Mirror mode<br>UEFI ARM Mirror<br>Memory Rank Sparing<br>Correctable Error Threshold<br>Run Sure<br>SDDC Plus One<br>ADDDC Sparing<br>Patrol Scrub<br>Interval | [Disable]<br>[Disable]<br>[Disable]<br>10<br>[Disable]<br>[Disable]<br>[Disable]<br>[Enable]<br>24 |                                                                                                                                                                               |

|                                                                                                                                                                                                |                                                                                                    | ++: Select Screen<br>14: Select Item<br>Enter: Select<br>+/: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESC: Exit |

7. Select *SDDC Plus One* and hit <Enter>. The options for SDDC Plus One will display as shown below. Using the arrow keys select *Enable* and hit <Enter>.

| Memory RAS Configuration Setup                                                                                                                                                                              |                                                                                 | Enable/Disable SDDC Plus One                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static Virtual Lockstep Mode<br>Mirror mode<br>UEFI ARM Mirror<br>Memory Rank Sparing<br>Correctable Error Threshold<br>Run Sure<br>SOOC Plus One<br>ADDOC Sparing<br>Patrol Scrub<br>Patrol Scrub Interval | [Disable]<br>[Disable]<br>[Disable]<br>10<br>SDDC Plus One<br>Disable<br>Enable | ++: Select Screen<br>14: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESD: Exit |

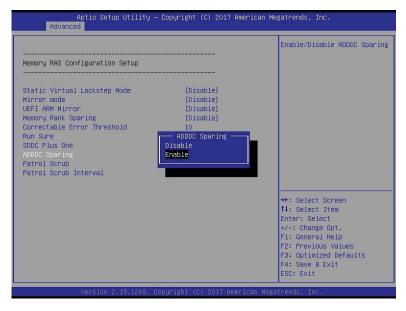

8. Scroll down to *ADDDC Sparing* and hit <Enter>. Select *Enable* and hit <Enter> as shown below.

9. Once you've set both items: *SDDC Plus One* and *ADDDC Sparing* to Enable, press the <F4> key on the top of your keyboard to save your configuration settings and exit the BIOS setup utility as shown below.

| Aptio Setup Utility – Copyright (C) 2017 American Me<br>Advanced                                                                                                                                                                                                            | gatrends, Inc.                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory RAS Configuration Setup<br>Static Virtual Lockstep Mode [Disable]<br>Mirror mode [Disable]<br>UEFI ARM Mirror<br>Memory Rank Sparing<br>Correctable Error Threshold<br>Run Sure<br>SDOC Plus One<br>A0000 Sparing<br>Patrol Scrub<br>Patrol Scrub Interval<br>Ves No | Enable/Disable ADDDC Sparing<br>++: Select Screen<br>11: Select Item<br>Enter: Select<br>+/-: Change Opt.<br>F1: General Help<br>F2: Previous Values<br>F3: Optimized Defaults<br>F4: Save & Exit<br>ESC: Exit |

| Version 2.19.1268. Copyright (C) 2017 American Mega                                                                                                                                                                                                                         | itrends, Inc.                                                                                                                                                                                                  |

10. Reboot your system for the new configuration settings to take effect.